## Oriental Motor Vexta PX243-03AA 2-Phase Stepping Motor

\$90.00

In Stock **Qtv Available: 10+ Used and in Excellent Condition**

**Open Web Page**

https://www.artisantg.com/64559-10

4 ARTISAN° TECHNOLOGY GROUP

Your **definitive** source for quality pre-owned equipment.

**Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

All trademarks, brandnames, and brands appearing herein are the property of their respective owners.

- Critical and expedited services

- In stock / Ready-to-ship

- · We buy your excess, underutilized, and idle equipment

- · Full-service, independent repair center

Artisan Scientific Corporation dba Artisan Technology Group is not an affiliate, representative, or authorized distributor for any manufacturer listed herein.

Revision 1.0

December 30, 1999

9605 Scranton Road Suite 700 San Diego, CA 92121-1773 3895 N. Business Center Drive Suite 100 Tucson, AZ 85705-6909

(858) 452-0020 · (858) 452-0060 (FAX) Web: www.synergymicro.com

## V452 /GRIG/ USER GUIDE

Copyright © 1997-1999 Synergy Microsystems, Inc.

This manual is copyrighted under Title 17 US Code of the United States Copyright Law. All rights are reserved by Synergy Microsystems, Inc. This document may not, in whole or in part, be copied, photocopied, reproduced, translated, scanned, or reduced to any electronic medium or readable form without the express written consent of Synergy Microsystems, Inc.

This document contains material of a proprietary nature to Synergy Microsystems, Inc. All manufacturing, use, and sales rights pertaining to this product are expressly reserved. Distribution of this material does not convey any license or title under any patent or copyright. It is submitted in strict confidence to provide technical information for purchasers of this product or for those considering the purchase of the product. Each recipient, by accepting this document, agrees that its contents will not be disclosed in any manner or any person except to serve this purpose.

Synergy Microsystems, Inc. reserves the right to make changes to the specifications and contents in this document without prior notification. If in doubt, users are urged to consult Synergy to determine whether any such changes have been made.

Synergy products are not intended for use in life support systems or other applications where a failure of the product could result in injury or loss of life. Customers using or selling this product in systems or applications serving such a function do so at their own risk and agree to fully indemnify Synergy Microsystems, Inc. for any and all damages arising from improper use.

This product and associated manuals are sold "AS IS" without implied warranty as to their merchantability or fitness for any particular use. In no event shall Synergy Microsystems, Inc. or anyone involved in the creation, production, or delivery of this product be liable for any direct, incidental, or consequential damages, such as, but not limited to, loss of anticipated profits, benefits, use, or to data resulting from the use of this product or associated manuals or arising out of any breach of warranty. In states that do not allow the exclusion or limitation of direct, incidental, or consequential damages, this limitation may not apply.

Synergy<sup>™</sup>, V452 Series<sup>™</sup>, V4xx Series<sup>™</sup>, V30 Series<sup>™</sup>, V20 Series<sup>™</sup>, R452<sup>™</sup>, and EZ-bus<sup>™</sup> are trademarks of Synergy Microsystems, Inc..

Synergy wishes to acknowledge that the names of products and companies mentioned in this manual are trademarks of their respective manufacturers.

PRINTED IN THE USA

# Manual overview

This manual is divided into the following sections that can be identified by an icon appearing on the upper outside corner of each page.

**1 - Overview** describes the models, options, features architecture, specifications and revisions made to V452 Series boards.

**2 - Getting Started** contains procedures for installing V452 Series hardware and hardware options.

**3 - Board Facilities** describes board-level functions and options including the addresses, interrupts, jumpers, control registers and default conditions.

**4 - Local Components** describe the operation of local bus components including the microprocessor, CPU mailbox, watchdog, RAM, and timer/counters.

**5 - Interface Options** describe the on-board circuitry that communicates with external devices including the EZ-bus, the serial I/O interface, the VMEbus interface and the System Controller.

**6 - Code Examples** contains programming examples for selected V452 Series components or processes.

**7 - Warranties & Service** provides complete information about Synergy product warranties and service.

**Appendix A — Cables & Connectors** describes the V452 cables and connectors.

**Appendix B — Specifications** lists the V452 specifications.

**Appendix C — Board Revision Summary** summarizes the V452 change history.

**Glossary & Index** defines terms used in the manual and provides an alphabetically arranged index.

Each manual includes the **V452 Series Quick Reference Card** which lists the in-formation you're likely to need for day-to-day use in a convenient shirt-pocket size.

# Table of contents

| Preface                                                    | Vi         |

|------------------------------------------------------------|------------|

| Manual revision summary                                    |            |

| Section 1, Overview                                        |            |

| V452 Series features                                       | 1-5<br>1-6 |

| Comparison: V440/V460 and V452 SBCs                        | 1-11       |

| Section 2, Getting Started                                 |            |

| Minimum system requirements                                | 2-3        |

| Installing a monitor PROM                                  |            |

| Installing the R452/R453 memory module                     |            |

| Installing/upgrading the R452/R453 memory module           |            |

| Setting up the V452 Series hardware                        | 2-17       |

| Default configuration                                      |            |

| Configuration tasks                                        |            |

| Enable/Disable Flash write<br>Set the VMEbus request level |            |

| Enable VME Slave remote reset                              |            |

| Select Round Robin or Priority request handling            |            |

| System controller                                          |            |

| Boot select, EPROM or onboard Flash                        |            |

| Installing V452 Series CPU boards                          |            |

| Power-on banners                                           |            |

| Setting up the V452 Series software                        |            |

| Default (pre-initialization) conditions                    |            |

| Section 3, Board Facilities                                | 2-30       |

| Address map                                                | 3_3        |

| Interrupts                                                 |            |

| Interrupts                                                 |            |

| Enabling/disabling interrupts                              |            |

| Interrupts on single vs. dual processor boards             | 3-11       |

| On-board interrupt sources                                 |            |

| Local bus timeout                                          |            |

| VMEbus interrupt handler                                   |            |

| Jumpers, switches, LEDs & Fuses                            |            |

| Jumpers                                                    |            |

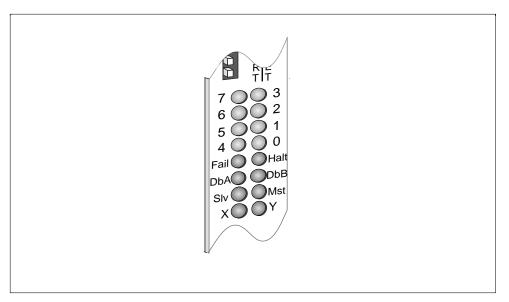

| Front panel                                                |            |

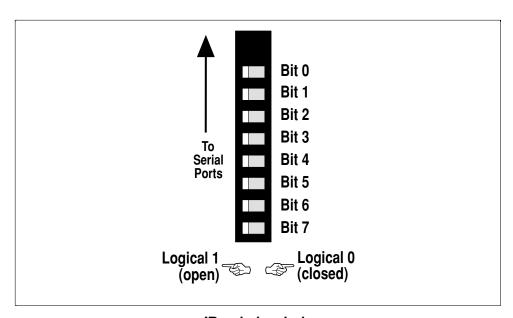

| 8-bit ID switch (front panel)                              | 3-30       |

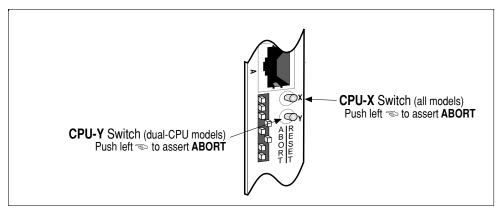

| Toggle switches                                            | 3-31       |

| LEDs                                          | 3-32 |

|-----------------------------------------------|------|

| Fuses                                         |      |

| V452 Series internal registers                | 3-35 |

| Status register                               |      |

| ID status register                            |      |

| Mode registers                                |      |

| Using Mode register functionsPrimary & Extend |      |

| Controlling the User LEDs                     | 3-42 |

| 2692 mode registers                           |      |

| VME interrupt vector register                 |      |

| Control registers                             |      |

| Primary & extended control registers          |      |

| Interrupt control registers                   | 3-52 |

| Slave interface control register              |      |

| Ethernet/VMEbus control registers             |      |

| Board information registers                   |      |

| Slot ID, FE39 0001                            |      |

| CPU & board type, FE39 0003                   |      |

| Memory size and installed options, FE39 4003. |      |

| Modifications and ECO level, FE39 8003        |      |

| PCB revision, FE39 C003                       |      |

|                                               |      |

| Default & reset conditions                    |      |

| Default conditions                            |      |

| Reset sources                                 |      |

| Reset sequence                                |      |

| Reset via software                            |      |

| VME Level 0 interrupt reset                   |      |

| Watchdog timer enable                         |      |

| Remote reset register                         | 3-07 |

|                                               |      |

| Section 4, Local Components                   |      |

| 68040 CPU                                     | 4-3  |

| Introduction                                  |      |

| Additional 68040 documentation                |      |

| Programming model                             |      |

| Instruction set overview                      |      |

| Exception processing                          |      |

| Operand transfer types                        |      |

| Bus snooping                                  |      |

| Memory management unit                        | 4-27 |

| 68060 CPU                                     | 4-31 |

| Introduction                                  |      |

| Additional 68060 documentation                |      |

| Programming model                             |      |

| Programmer's model differences: 68060 vs. 680 |      |

| Data type differences: 68060 vs. 68040        |      |

| Addressing mode differences: 68060 vs. 68040  | 4-37 |

| Instruction set overview                      |      |

| Integer unit                                  |      |

| Exception processing                          |      |

| Exception differences: 68060 vs. 68040        | 1.11 |

|          | Instruction and data caches         |       |

|----------|-------------------------------------|-------|

|          | Cache differences: 68060 vs. 68040  |       |

|          | Cache organization                  |       |

|          | Cache coherency                     |       |

|          | Setting up the 68060 caches         |       |

|          | Paged memory management unit (PMMU) |       |

|          | PMMU differences: 68060 vs. 68040   |       |

|          | PMMU architecture summary           | 4-49  |

| CPU      | Mailbox                             | 4-51  |

|          | Mailbox memory areas                | 4-51  |

|          | Mailbox interrupts                  | 4-53  |

| CPU '    | Watchdog                            | 4-57  |

| Dyna     | mic RAM                             | 1.63  |

| Бупа     | DRAM access optimization            |       |

|          | DRAM tuning strategies              |       |

|          | Memory parity                       |       |

|          | Clearing the parity error bit       | 4-68  |

|          | Detecting & isolating bad parity    | 4-68  |

|          | Multi-port memory contention        |       |

|          | DRAM address decoding               | 4-70  |

|          | R452/R453 memory modules            | 4-72  |

| EPRO     | DM                                  | 4-73  |

|          | Selecting the monitor EPROM type    |       |

|          | Flash EPROM configuration           |       |

|          | EPROM use                           |       |

|          | Flash considerations                | 4-77  |

| Flash    | memory module                       | 4-79  |

|          | Installing the Flash module option  |       |

|          | Accessing the Flash module          |       |

|          | Block organization                  |       |

|          | Flash considerations                | 4-83  |

| Onbo     | oard flash memory                   |       |

|          | Introduction                        |       |

|          | Writing and erasing                 |       |

|          | Block organization                  |       |

|          | Booting from onboard Flash          | 4-87  |

| Timer    | rs & counters                       |       |

|          | 16-bit timers (2692)                | 4-91  |

| Clock    | k calendar                          | 4-101 |

| Non-v    | volatile 8K x 8 SRAM                | 4-105 |

| 1 1011 1 | Replaceable battery                 |       |

|          |                                     |       |

| C1'      | ion E Interface Ontions             |       |

| Secti    | ion 5, Interface Options            |       |

| Asyno    | chronous serial interface           |       |

|          | P2 access to serial interface       | 5-6   |

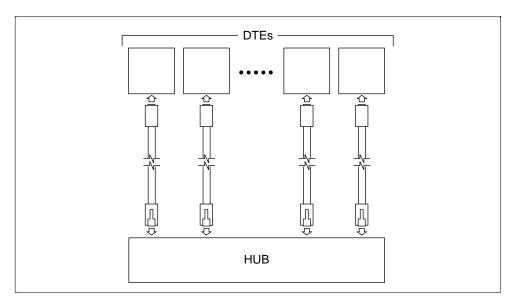

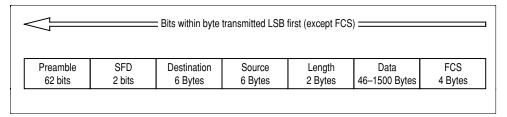

| Etheri   | net 10Base-T interface option       | 5-7   |

|          | Introduction                        |       |

|          | Ethornot notwork connections        | 5.0   |

| Ethernet ID                                                                 | 5-11          |

|-----------------------------------------------------------------------------|---------------|

| Avoiding bus contention — CSMA/CD                                           | 5-11          |

| Interchange signals                                                         |               |

| Address map                                                                 |               |

| Interrupts and vectors                                                      |               |

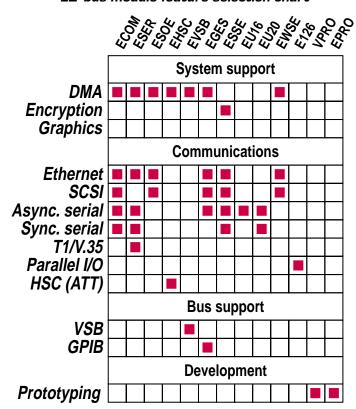

| EZ-bus interface                                                            |               |

| EZ-bus modules                                                              |               |

| VME Slave interface                                                         |               |

| Setting up the VME Slave interface                                          |               |

| Configuring Slave write access memory protection                            |               |

| Enabling/disabling the Slave interface                                      | 5-31          |

| Multi-port memory access contention                                         |               |

| VME Slave block transfer (BLT)                                              |               |

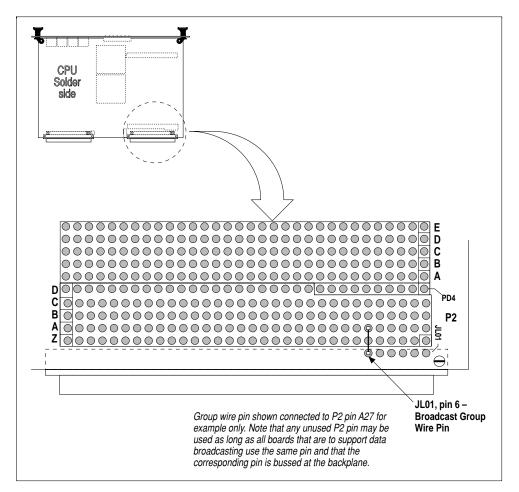

| Data broadcasting                                                           |               |

| Hardware setup for data broadcasting                                        |               |

| Setting up data broadcasting groups<br>Enabling/disabling data broadcasting |               |

| Configuring a sample data broadcast group                                   |               |

| VME Master interface                                                        |               |

| Setting up the Master interface                                             |               |

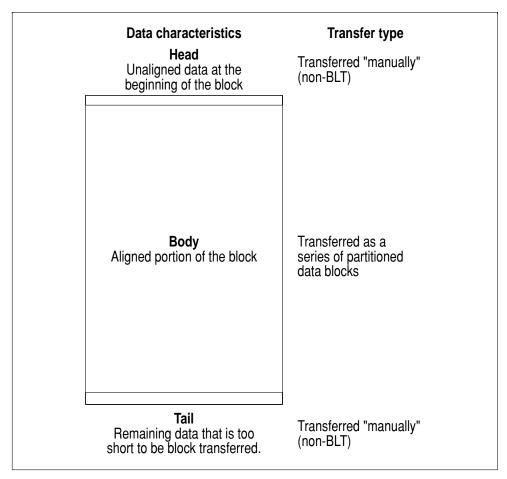

| VME Master data transfer bandwidth                                          | 5-51          |

| VME Master BLT                                                              | 5-53          |

| System Controller                                                           |               |

| Forcing system controller                                                   | 5-66          |

| Configuring the bus arbiterVMEbus arbitration timeout                       |               |

| Configuring the bus error timeout interval                                  |               |

| Enabling VME SysFail interrupts                                             |               |

| , , ,                                                                       |               |

| Section 6, Code Examples                                                    |               |

| Programming differences                                                     | 6-3           |

| Block transfer (BLT) with DMA example                                       | 6-5           |

| Flash EPROM programming tools                                               | 6-15          |

| Timer code examples                                                         | 6-25          |

| 2692 DUART code example                                                     | 6-33          |

| Section 7, Warranties & Service                                             |               |

|                                                                             | 7.3           |

| Warranty terms & options                                                    |               |

| Customer service                                                            | . <b></b> 7-5 |

#### Table of contents

## **Appendices**

| Appendix A, Cables & Connectors          | A-1    |

|------------------------------------------|--------|

| VMEbus connectors (P1 & P2)              | A-3    |

| EZ-bus connectors (P3 & P4)              | A-5    |

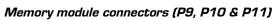

| Memory module connectors (P9, P10 & P11) |        |

| Ethernet 10Base-T connector (P8)         | A-11   |

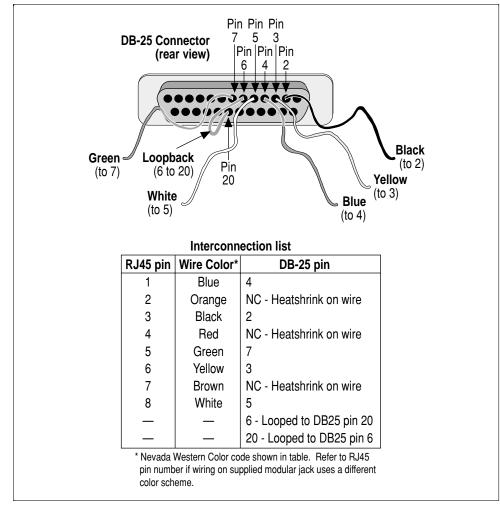

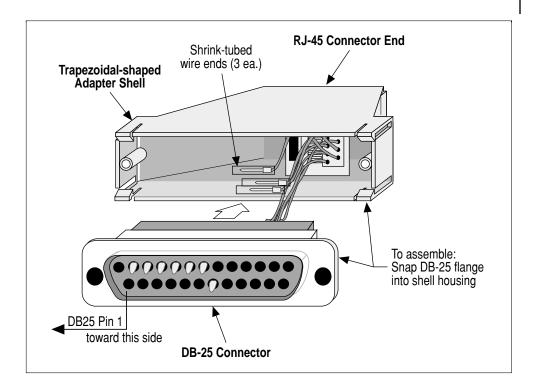

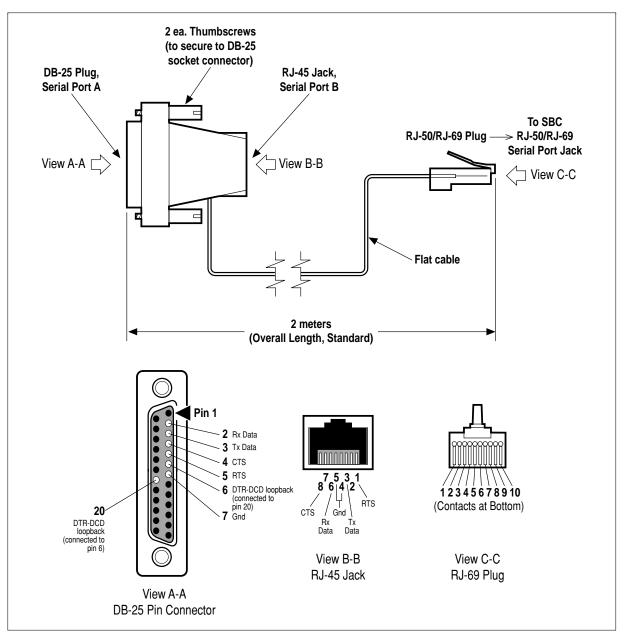

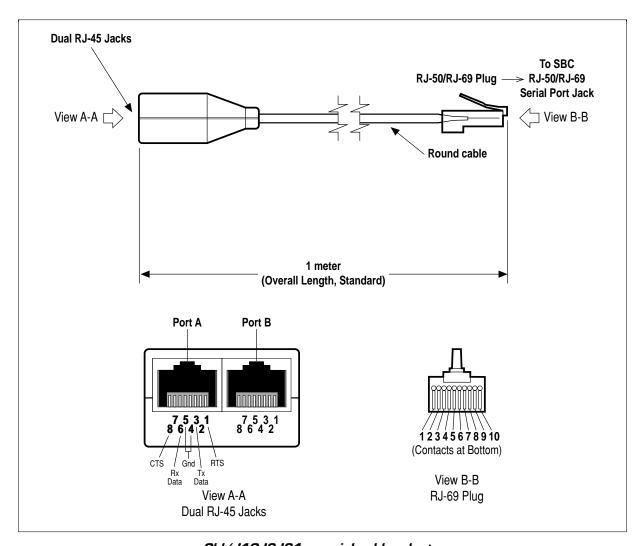

| Asynchronous serial connectors (P5-P7)   |        |

| Serial I/O cabling options               |        |

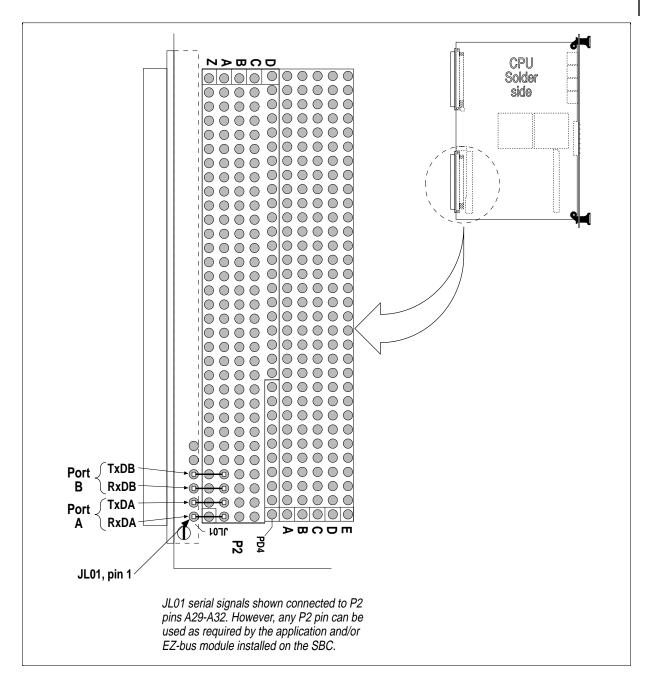

| P2 serial interface option               | A-29   |

| Appendix B, Specifications               | B-1    |

| VMEbus compliance                        | B-1    |

| Physical dimensions                      |        |

| Weight                                   |        |

| Power requirements                       |        |

| Operating environment                    |        |

| Number of slots                          |        |

| Board layout                             | B-3    |

| Appendix C, Board Revision Summary       | C-1    |

| ,                                        |        |

| Glossary & Index                         |        |

| Glossary                                 | Glos-1 |

| Index                                    | Indx-1 |

# Preface

This manual provides detailed information on how to install, configure, and operate the V452 Series of single-board computers (SBCs). This chapter will help you use the contents of this document to your best advantage. It is designed to help you:

• evaluate the V452 Series for purchase:

To aid your buying decision, the *Overview* contains pertinent information to help you determine if the V452 Series meets the needs of your system design. These chapters include technical descriptions, a list of features, and general specifications.

• start up your V452 Series board:

**Getting Started** contains the information you need to install your system for the first time. It outlines minimum system requirements, configuration checklists and installation procedures.

For previous customers of Synergy CPU boards, the *Getting Started* section also includes a chapter that highlights new product features and describes the primary operational differences between V452 Series boards and Synergy's V30 Series and V20 Series boards.

• answer technical questions about the V452 Series:

The *Board Facilities, Local Components,* and *Interface Options* sections form an in-depth reference for using the V452 Series and peripherals.

Often-used information is included in a pull-out *V452 Series Quick Reference Card*.

# Typographical conventions

This manual observes the following conventions:

- The term V452 Series is used in conjunction with information that applies to ALL models of the board series. When differences among models exist, specific model numbers are used to described any special features.

- 2 In diagrams and descriptions in this manual, signal names followed by a backslash (\) are active low.

V452 User Guide

# Related publications

Special attention has been paid to making this manual as complete as possible to minimize the number of times you may need to reference other manuals. However, should you need additional information, the following books expand on several related topics:

#### Synergy publications

- ✓ V4xx Series 68040 VME Single Board Computer User guide describes the features, installation, and operation of Synergy's V4xx Series of CPU boards.

- V30 Series 68030 VME Single Board Computer User guide describes the features, installation, and operation of Synergy's V30 Series of CPU boards.

- V20 Series 68020 VME Single Board Computer User guide describes the features, installation, and operation of Synergy's V20 Series of CPU boards.

- Datasheet Supplement, VME CPU Version contains reprints of selected portions of the manufacturer's datasheets for major components used on Synergy VME SBCs. Each included datasheet appears in the Datasheet Supplement courtesy of their respective manufacturers.

- EZ-bus™ Designer's Guide describes the functions and specifications of the Synergy EZ-bus. All Synergy VMEbus SBCs include two EZ-bus connectors allowing the connection of up to two EZ-bus interface or I/O modules. This manual describes all of the available daughter modules and the necessary mechanical and interface information required to create new modules that are compatible with the EZ-bus.

- SMon User Guide describes Synergy's monitor PROM and application development/debugger software. SMon provides a powerful cross-plaform development environment with full support for host/target communication over a TCP/IP Ethernet network.

#### IC manufacturer's publications

- M68060™ Microprocessor User's Manual; Rev. 1; Motorola® (520) 994-6561.

- MC68040™ Enhanced Microprocessor User's Manual; 2nd Edition; Prentice Hall® or Motorola® (520) 994-6561.

- MC68000PM/AD, MC68000 Programmer's Reference Manual; Prentice Hall® or Motorola® − (520) 994-6561.

- MC68881/MC68882™ Floating Point Co-processor User's Manual;

2nd Edition; Prentice Hall or Motorola.

#### VMEbus specification & publications

- The VMEbus™ Specification; Rev D.1; VMEbus International Trade Association (VITA) (602) 951-8866.

- The VMEbus™ Handbook; 2nd Edition; VMEbus International Trade Association (VITA) (602) 951-8866.

#### Software manufacturer's publications

- pSOS<sup>+</sup>/68k™ Evaluation Package User's Guide; Software Components Group; (408) 437-0700.

- Using Professional OS9, Microware Systems Corporation

- VxWorks™ Reference Manual; Version 5.1; Wind River Systems®;

(800) 545-WIND.

V452 User Guide

# Manual revision summary

| Revision level | Revision date | Section | Affected chapter/description                                         |

|----------------|---------------|---------|----------------------------------------------------------------------|

| 1.0a           | 12/21/96      |         | 1st preliminary release                                              |

| 1.0b           | 3/26/97       |         | 2nd preliminary release                                              |

| 1.0c           | 1/8/99        |         | 3rd preliminary release                                              |

|                |               |         | Section 3/Corrected configuration jumper information for Flash Boot. |

| 1.0d           | 5/24/99       |         | 4th preliminary release                                              |

|                |               |         | Section 0, Section 9/Revised for new telephone area code.            |

| 1.0            | 12/30/99      |         | Initial GA release.                                                  |

The following chapters introduce the  $V452\ Series$  of single-board computers.

V452 Series features

• Comparison: V440/V460 and V452

V452 User Guide 1-1

# V452 Series features

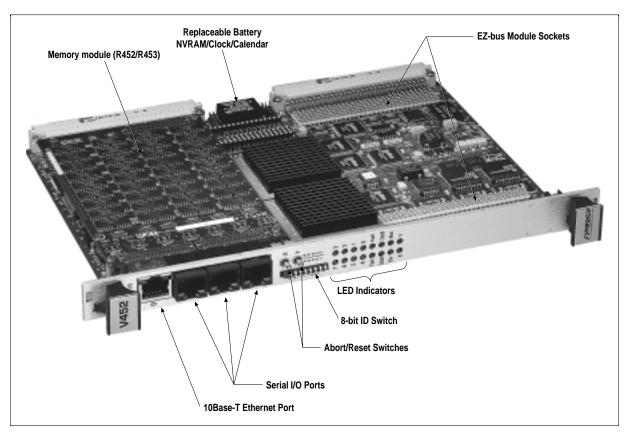

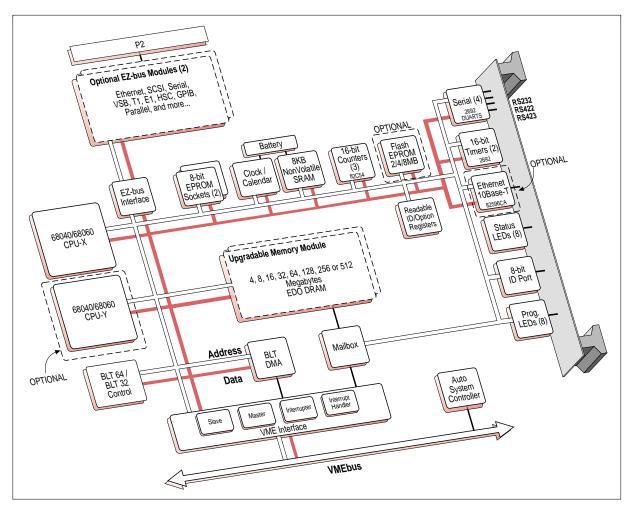

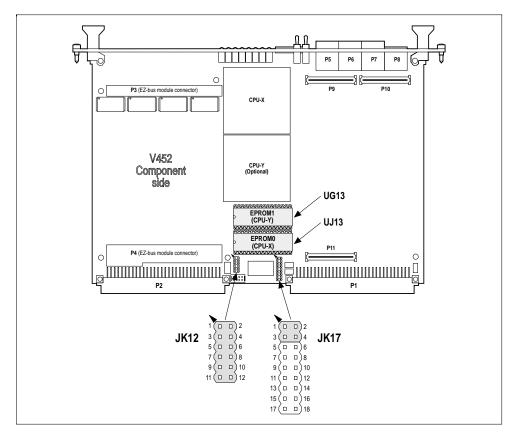

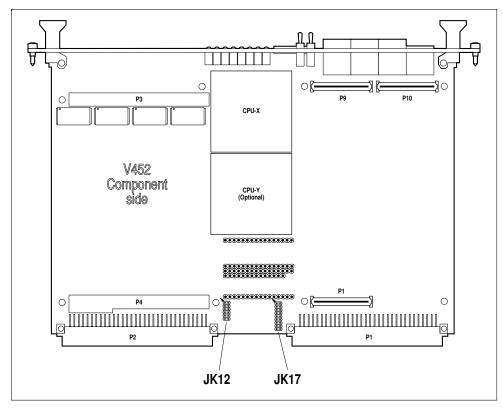

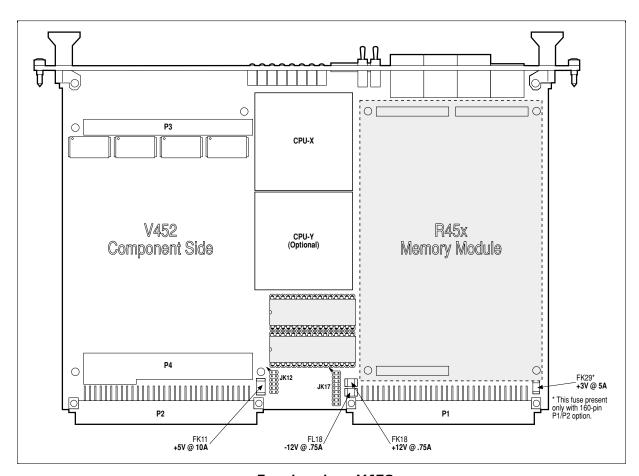

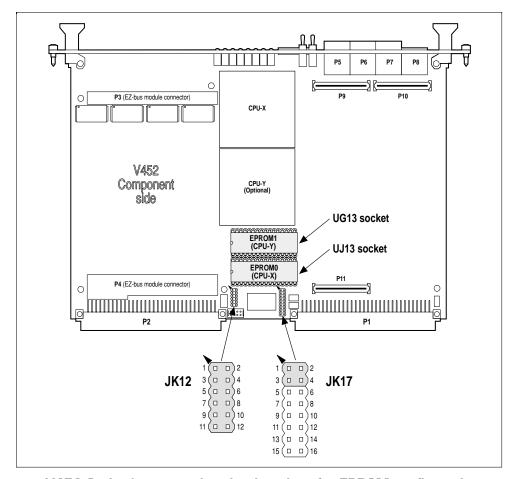

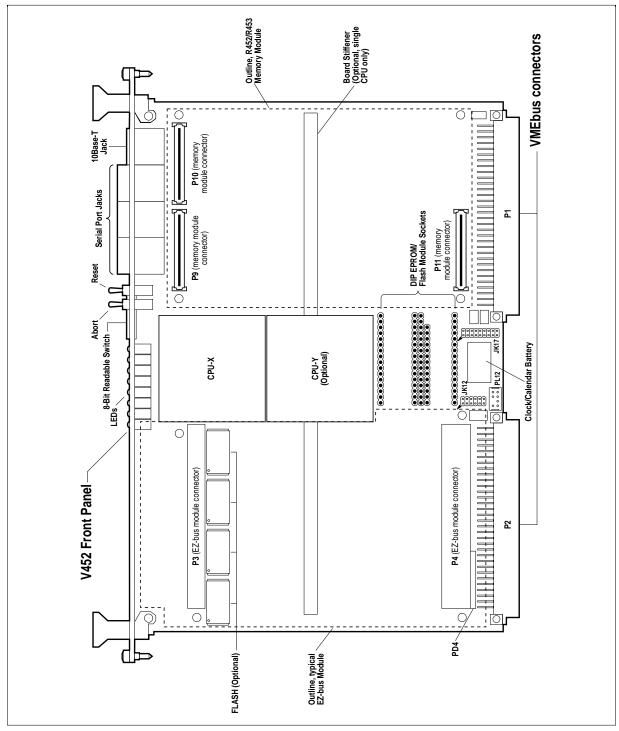

The V452 Series are high-performance, VMEbus-compatible single board computers (SBCs) using single or dual Motorola **MC68040 or MC68060 microprocessors**. The general component side layout of the V452 SBC is shown below.

V452 Series single board computer

V452 User Guide 17-3

#### V452 Series models & features

The V452 Series offers flexibility and performance to satisfy a wide range of applications. Standard features include low power operation, Bellcore/Nynex compliant design, auto system controller, and VME64 extensions support.

The V452's **EZ-bus** interface is a high-performance daughter module bus that supports DMA burst accesses to motherboard memory. The EZ-bus interface affords valuable configuration flexibility for your system designs. All necessary signals and a 32-bit data bus are provided to implement many optional features including:

- VSB interfaces

- Ethernet, SCSI and/or serial interfaces

- custom P2 I/O

- multiple serial ports and other uses

Standardized and custom-designed daughter modules are also available providing true single-board solutions for a wide range of processing and interface needs. The V452 is provided with an enhanced EZ-bus that accommodates PCI bus-based devices on the EZ-bus module. This broadens the range of EZ-bus solutions to meet the requirement of most any application.

A full line of system **monitor**, **kernal**, and **operating system** software/ firmware is also available from Synergy and leading developers.

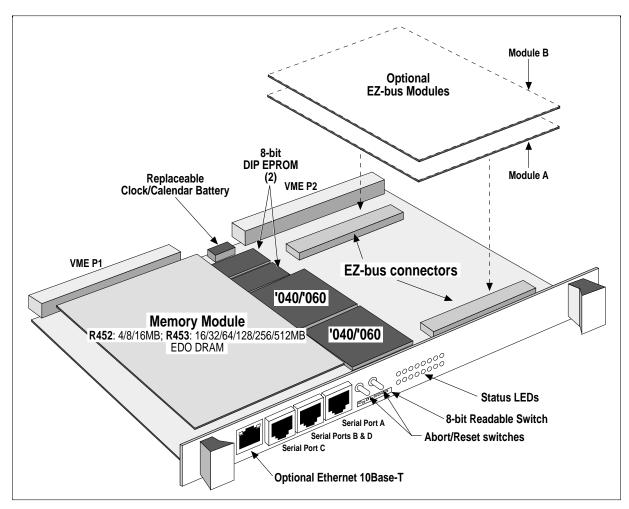

# Physical configuration

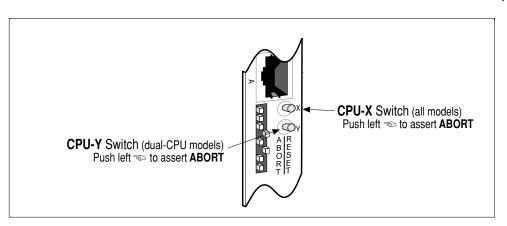

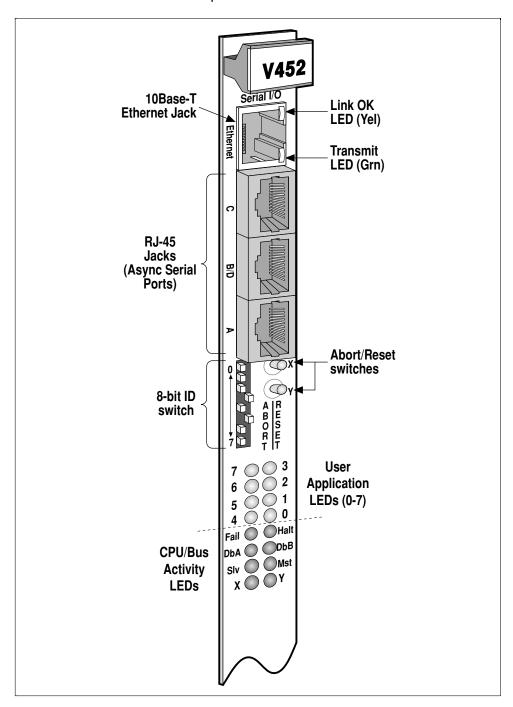

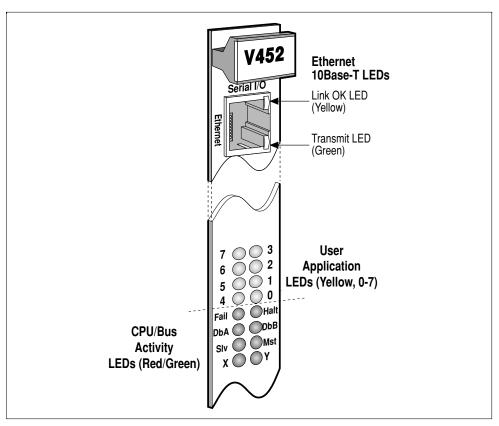

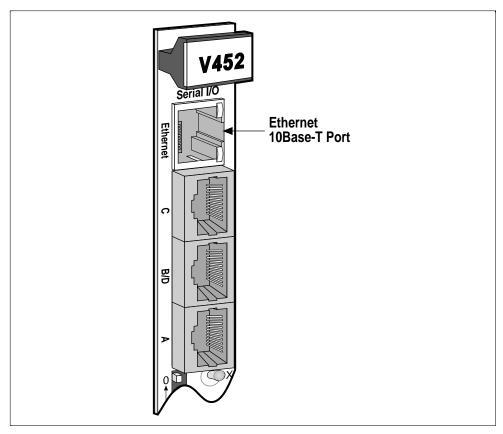

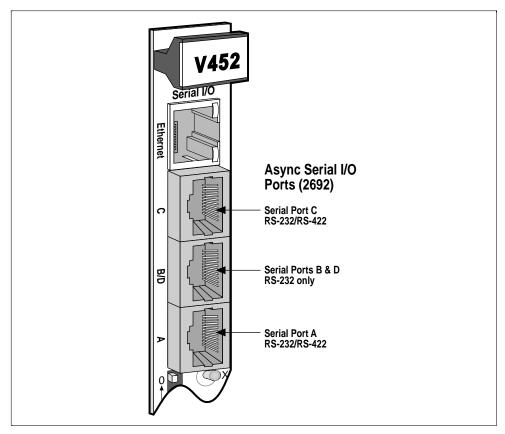

The V452 SBC uses a 6U VME form factor. Onboard connectors are used to attach modular memory and I/O options (EZ-bus modules). Four RJ-45 jacks are mounted on the front panel; one is for the optional Ethernet 10Base-T port with the remainder providing 4 serial ports (serial ports B and D share a jack). Also on the front panel are abort & reset switches, 16 status LEDs, and a readable 8-bit DIP switch.

V452 configuration

V452 User Guide 1-5

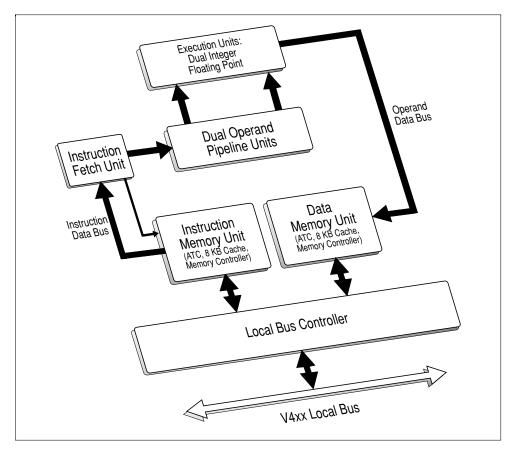

# Functional block diagram

The figure below shows the functional block diagram for the V452 SBC.

V452 functional block diagram

# Feature summary

The V452 Series provides the following list of powerful features and functions that are common to all of the boards in the V452 Series product line:

#### **CPU**

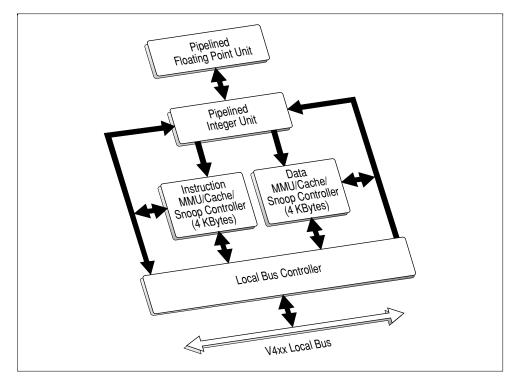

- Motorola® 68040 32-bit CPU(s) featuring 16 32-bit registers, independent internal 4KB instruction & data caches, a 19/25 MIPS processor core, a built-in 3.6/4.7 MFLOPS floating-point and integer coprocessor, and a 25/33 MHz CPU clock speed.

- Motorola® **68060** 32-bit CPU(s) featuring a RISC-like architecture that includes branch prediction logic and superscalar pipelines. The '060 is user object code compatible with the 68040 and all previous 68K processors. Compatibility is assured through the use of dual '040-compatible CPU integer cores, an '040-compatible floating point core, 8KB instruction and data caches, an '040-compatible paged memory management unit, and bus controller. The processor runs internally at **50/66** MHz with external bus operation at **25/33** MHz.

#### Memory

- 4, 8, 16, 32, 64, 128, 256 or 512 MB of EDO dynamic RAM with a 32-bit data path on modular daughter modules for configuration flexibility and for easy memory upgrades in the field.

- Support for the 68040 optimized burst mode.

- EDO DRAM (Extended Data Out DRAM) reduces DRAM cycle time yet provides valid data for much longer time for increased read/write access performance over conventional DRAM designs.

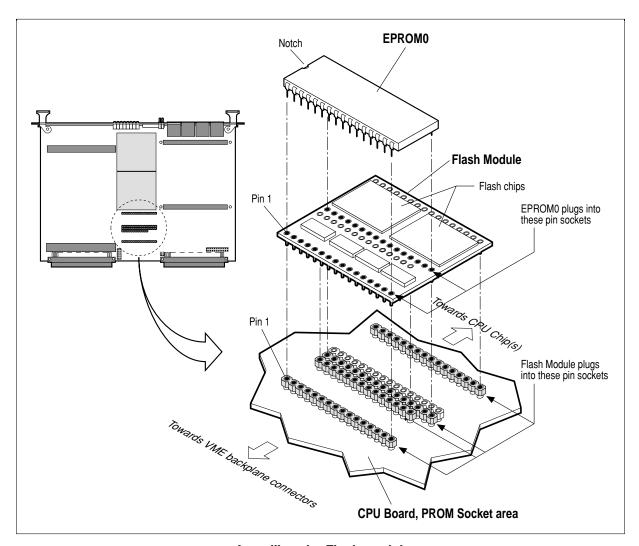

- Two independent 32-pin **EPROM** sockets provide up to 2 MB of PROM Monitor space consisting of EPROM, FLASH EPROM or a combination of these devices. These sockets also accept special modules that provide up to 16 MB of Intel FlashFile™ memory in addition to the normal 1 MB space allocated for the boot EPROM.

- Optional 2/4/8 MB of onboard Intel FlashFile™ memory.

V452 User Guide 1-7

#### Construction

- Bellcore/Nynex-compliant construction.

- Ruggedized option (single CPU only) available.

- Optional conformal coat.

#### **VMEbus**

- **BLT64** Master/Slave Block Transfers (BLT) DMA to **72 MB/sec** supporting VME Specification Revision D.1.

- BLT32 Master/Slave Block Transfers (BLT) DMA support for transfers up to 33 MB/sec.

- Supports the **bus snooping** for write accesses to local memory via the VMEbus Slave interface.

- VME interface supports A32/24/16 and D32/16/8 in Master mode; A32/24 and D32/16/8 in Slave mode.

- VMEbus requester supports Release-When-Done (RWD) or Release-On-Request (ROR) for bus release and FAIR bus request arbitration.

- VMEbus **priority request level** is software or jumper-selectable at 4 different priority levels.

- Automatic System Controller lets the SBC configure itself automatically as the System Controller when installed in slot 1. The System Controller provides prioritized and/or round-robin arbitration, bus arbiter timeout, and a programmable VMEbus grant timeout period. The System Controller is isolated for continued operation in the unlikely event of a failure elsewhere on the board. The System Controller circuit is able to assert the VMEbus Reset signal under software control without causing a local reset of itself. A jumper is provided to disable the automatic System Controller feature to ensure compatibility with other boards in the system.

- Software programmable VME Slave interface featuring a Slave access window size equal to installed memory that can be assigned to any location within the entire 4 GByte VME address space.

- Supports unaligned VMEbus transfers.

- Software-controllable data broadcast mode for simultaneous data transfers to multiple VME Slaves.

- Supports remote reset under software control by a remote VME Master.

- Standard 6U VME card format with VMEbus P1 and P2 connectors.

#### VME64 extensions

- Supports Auto System Controller.

- Supports readable System ID and configuration.

- Optional wide 160-pin P1 and P2 connectors for VME64 style I/O and 3V Vcc backplane.

#### Interrupts

- Software-controllable **interrupt reception** for on-board interrupt sources via programmable register.

- Programmable **interrupt level assignments** for on-board interrupt sources via a socketed Programmed Array Logic (PAL) device.

- VMEbus interrupter can assert interrupts at any level under software control.

- VME **interrupt handler** for any group of up to 7 VMEbus interrupt priority levels.

- Interrupt-driven CPU Mailbox for inter-CPU and inter-process communications.

- Remote reset via VME writeable register.

- Watchdog timer can reset board if software hangs or halts.

- Local bus time-out circuit asserts a local bus error to the CPU when individual data transfers across the local bus take longer than 30 microseconds.

V452 User Guide 7-9

#### Peripherals

- Four RS-232/RS-423 single-ended, or 2 RS-422A differential and 2 RS-232/RS-423 single-ended serial channels for asynchronous serial communication up to 38.4K baud terminating in three RJ-45 10-pin connectors on the front panel.

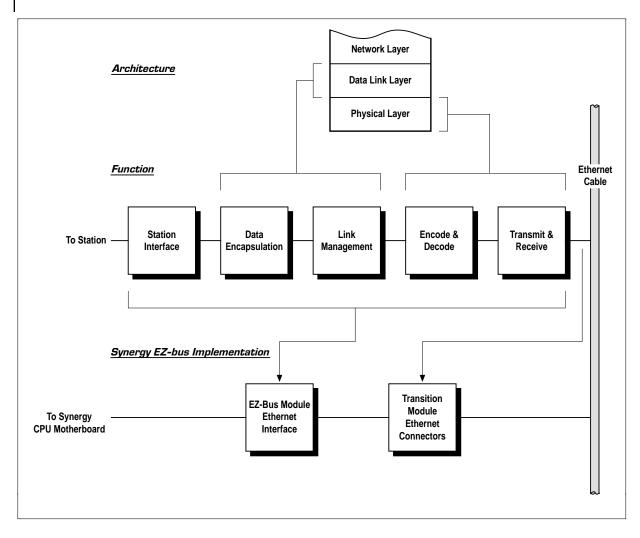

- Optional onboard 10Base-T Ethernet port.

- EZ-bus daughterboard interface is provided for custom P2 I/O, including VSB, memory expansion, SCSI, Ethernet, or high-speed floating point coprocessor. Synergy offers a standard set of off-the-shelf boards or can custom design for specialized needs. Customers may design their own daughter modules by using the EPRO/VPRO prototype board and the EZ-bus Designer's Guide, both available from Synergy. The V452 EZ-bus interface supports PCI-like initiator-throttled DMA accesses.

#### System timer/counter facilities

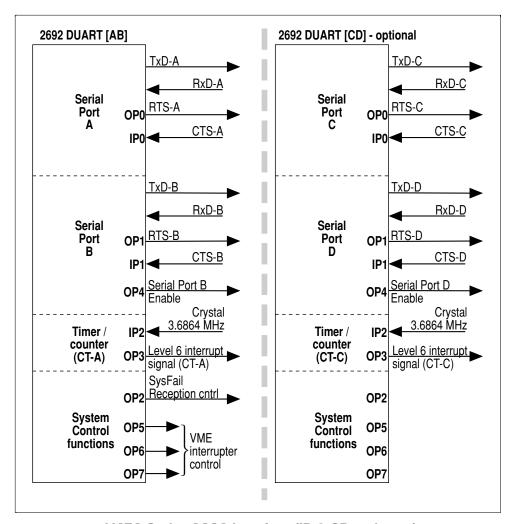

- Five **16-bit counter/timers** with interrupt support. The two timers from the two **2692** chips feature prescalers. The three counters from the **82C54** chip allow *on-the-fly* counter readings.

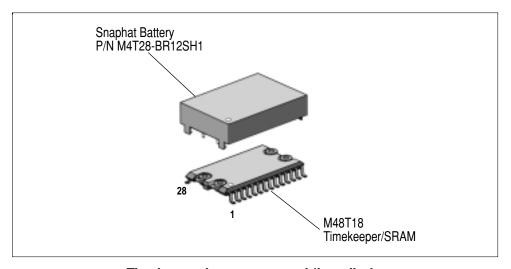

- **Time-of-day** clock/calendar with 8KB of non-volatile RAM for general use and with user-replaceable battery. ■

#### User interface

- Eight front panel **user-programmable** LEDs indicating application events and conditions.

- Eight front panel status LEDS indicating the HALT and/or SysFail status of the on-board CPUs, whether the V452 Series board is currently operating as the VMEbus Master, or whether an on-board CPU(s), EZ-bus module or an external VMEbus Master is in control of the local bus.

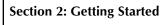

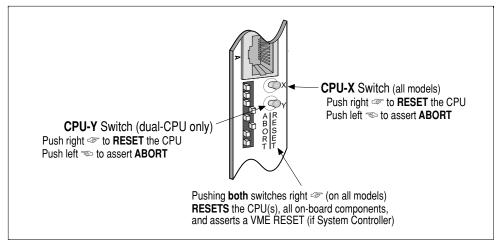

- **RESET** toggle switches can assert a CPU, board, and/or VMEbus level RESET signal; nmi **ABORT** switch for each on-board CPU.

- Front panel Link and Transmit status LED indicators for optional onboard 10Base-T Ethernet port.

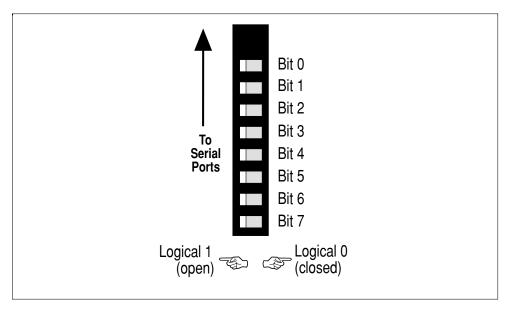

- Eight position software-readable ID switch for processor identification or option selection.

# Comparison: V440/V460 and V452 SBCs

For information reference, this chapter summarizes key differences between the Synergy Microsystems V440/V460 and V452 SBCs.

#### **Memory Architecture**

- V440/V460 maximum of 64MB w/double-stacked memory module using EDRAM chips

- V452 maximum of 512MB w/quad-stacked memory module using EDO DRAM chips

#### **Low Power**

- V440/V460 not originally designed for low power

- V452 designed from ground up for low power

#### **EZ-bus interface**

- V440/V460 conventional (non-enhanced) EZ-bus

- ▼ V452 enhanced EZ-bus; accommodates PCI-bus based chips on EZ-bus module for wider selection of I/O options

#### Flash

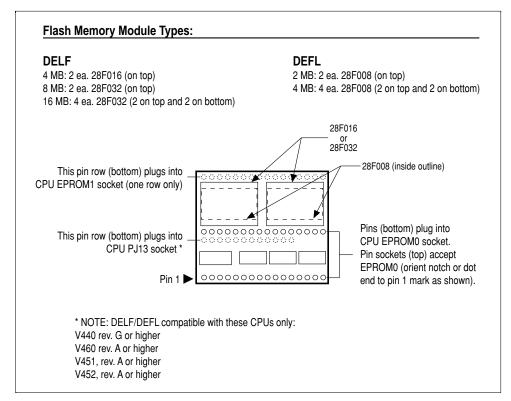

- ▼ V440/V460 optional Flash EPROM option (512KB max.) or Flash memory module (DELF/DEFL) up to 16MB

- V452 optional onboard 2/4/8MB Flash or Flash memory module (DELF/DEFL) up to 16MB

V452 User Guide 1 = 1 1

Comparison: V440/V460 and V452 SBCs

#### **RTC NVRAM and Battery**

- V440/V460 2KB NVRAM; battery not user replaceable

- V452 NVRAM, 8KB (user-selectable) or 2KB (default) for compatibility with pre-V45x SBCs; battery user replaceable

#### **Bellcore/Nynex compliance**

- V440/V460 not compliant

- V452 compliant (no parts on rear, no parts under parts, no dissimilar metal connectors, minimal use of sockets and jumpers)

#### **Ethernet interface**

- V440/V460 needs optional EZ-bus module support for AUI, 10Base-2, 10Base-T

- V452 optional onboard 10Base-T port accessible from front panel and P2 user I/O

#### **CPU Support**

- V440/V460 single or dual '040 or '060 (provided as V450)

- V452 single or dual '040 or '060

#### Ruggedized

- V440/V460 not available

- V452 option available for single CPU boards only

#### **Auto System Controller**

- V440/V460 not available

- V452 comes standard

#### VME64 extensions support

- V440/V460 not available

- V452 comes standard with auto system controller and readable system ID; wide (160-pin) P1/P2 available as option

#### **Conformal coat**

- V440/V460 not available

- V452 available as option

#### Front panel with EMI shielding

- V440/V460 not available

- V452 available as option

#### Readable board information register

- V440/V460 not available

- V452 comes standard (indicates slot ID; CPU and board type; memory size and installed options; Mods/ECO level; and PCB revision)

#### VMEbus request level

- ✓ V440/V460 jumper selectable

- V452 jumper and software selectable

#### Serial I/O via P2 connector

- V440/V460 supported (TxD, RxD, and handshaking signals)

- V452 supported (TxD and RxD signals only)

V452 User Guide 1-13

**Section 1: Overview**

Comparison: V440/V460 and V452 SBCs

2

This section provides configuration, setup and general information for the V452 SBC.

- Minimum system requirements

- Installing a monitor EPROM

- Installing the R452/R453 memory module

- Setting up the V452 Series hardware

- Installing V452 Series CPU boards

- Setting up the V452 Series software

V452 User Guide **2-1**

# Minimum system requirements

The following system components are required to install and test V452 Series boards:

◆ 6U VMEbus-compatible card cage with P1 backplanes installed — A card cage with forced air cooling is required. In addition, if 64 or 32-bit addresses or 64 or 32-bit (BLT or D32) data transfers are to be used, a P2 backplane must also be installed.

V452 Series boards feature state-of-theart, high-speed, transfers across the VMEbus that in some cases may approach the maximum VME specifications for transfer speeds. As a result, to support these transfers the underlying connectors, circuitry, and PCB boards used in the VME card cage must be constructed of high-quality materials that are fully-compliant with VME specifications.

For example, VME card cages containing 10-layer, PCB boards are normally required to support high-speed VME transfers. Older style, card cages containing 6-layer boards may have some difficulty conducting these signals without generating excessive noise.

V452 User Guide 2-3

#### **Section 2: Getting Started**

#### Minimum system requirements

Pin row **B** of the P2 backplane is defined by VMEbus specifications and is bussed across the entire backplane. Pin rows **A** and **C** are user configured and, if connected at all, are normally connected to adjacent slots via wirewrap or special cables.

Because the P2 pinout may vary between backplanes or even slots in the same backplane, DO NOT INSTALL the V452 Series into a system slot whose P2 backplane is not compatible with the V452 Series' P2 pinout. Failure to observe this warning can cause the complete destruction of many on-board components and also voids the product warranty.

The V452 Series pinout meets standard VME specifications for row **B**, but rows **A** and **C** will vary according to the EZ-bus daughterboard installed. Daughterboard pinouts are shown in the associated daughterboard manual. If no daughterboard is present, P2 backplane rows **A** and **C** are defined as **no-connects**.

For a complete list of the V452 Series P2 assignments, see the *VMEbus connectors* (*P1-P2*) chapter in Appendix A.

Power supply \_ Standard V452 Series boards require the following power supply voltage levels:

#### V452 single processor, typical power consumption:

'040/33 MHz with 16MB DRAM:

$+5.0v \pm 5\% = 3.4 \text{ Amps}$

$-12.0v \pm 5\% = 30 \text{ mA}$

'060/50 MHz with 16MB DRAM:

$+5.0v \pm 5\% = 3.0 \text{ Amps}$

$-12.0v \pm 5\% = 30 \text{ mA}$

#### V452 dual processor, typical power consumption:

'040/33 MHz with 16MB DRAM:

$+5.0v \pm 5\% = 4.1 \text{ Amps}$

$-12.0v \pm 5\% = 30 \text{ mA}$

'060/50 MHz with 16MB DRAM:

$+5.0v \pm 5\% = 3.8 \text{ Amps}$

$-12.0v \pm 5\% = 30 \text{ mA}$

Ensure that the power supply is capable of meeting the above requirements plus the requirements of any additional boards in the system. An extra 20% margin of current capacity should be factored in for safety.

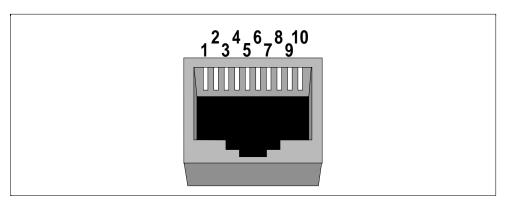

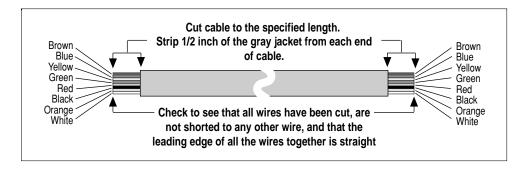

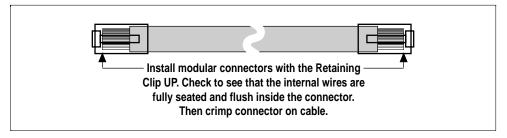

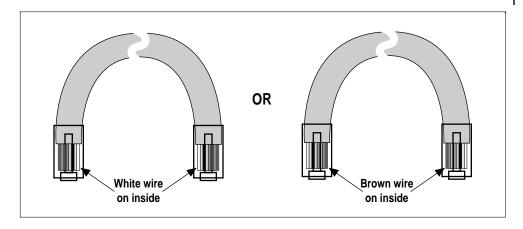

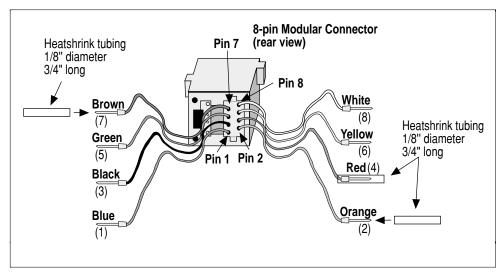

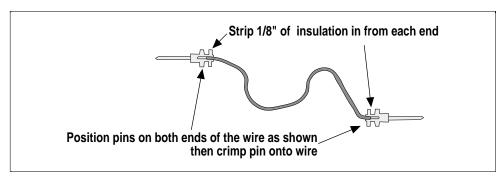

- One modular serial I/O cable (and Modular-to-D adapter if necessary) The serial ports on V452 Series boards use 10-pin modular telephone-type (AT&T) connectors. A Modular-to-D adapter is required to connect the modular jacks to serial devices (e.g, terminals) that have D-type serial connectors. Additionally, the use of both Serial Ports B and D require the use of a special adapter. Refer to the **Serial cabling options** chapter in Appendix A.

- RS-232 compatible video display terminal

V452 User Guide 2-5

## **Section 2: Getting Started**

### Minimum system requirements

# Installing a monitor PROM

V452 Series boards provide two, 32-pin, 8-bit, DIP EPROM sockets that can accept any combination of the following devices:

- 27C010 1 Mbit EPROM (128 KB)

- 27C020 2 Mbit EPROM (256 KB)

- 27C040 4 Mbit EPROM (512 KB)

- 27C080 8 Mbit EPROM (1 MB)

- 28F010 1 Mbit Flash EPROM (128K x 8, 256 KB)

- 28F020 2 Mbit Flash EPROM (256K x 8, 512 KB))

Normally, all boards ship from the factory with the appropriate monitor PROM already installed, however new or updated PROMs can also easily be added or changed in the field.

The paragraphs below describe a field installation of a new EPROM and all of the potential configuration changes you may need to make to the V452 Series CPU board as a result:

If the desired monitor PROM(s) is(are) already present on the V452 Series board, proceed to the next chapter in this section.

If the optional Flash memory module is to be installed instead of EPROM(s), or for information about the Flash memory module itself, see the *Flash memory module* chapter in Section 4.

V452 User Guide 2-7

## Materials

To complete this procedure, you will need the following materials:

- The desired monitor firmware PROM(s),

- A chip extractor tool to remove the current PROM (if necessary),

- The manual for the software product on the new EPROM.

# Procedural steps

To install a monitor EPROM, complete the following procedure:

• Verify proper operation of the motherboard (if replacing an existing monitor PROM) — Before attempting to install a new EPROM on an existing board, consider checking that the motherboard (and any attached daughterboards) are operating properly by performing the installation/checkout procedure for the V452 Series board as described later in this section.

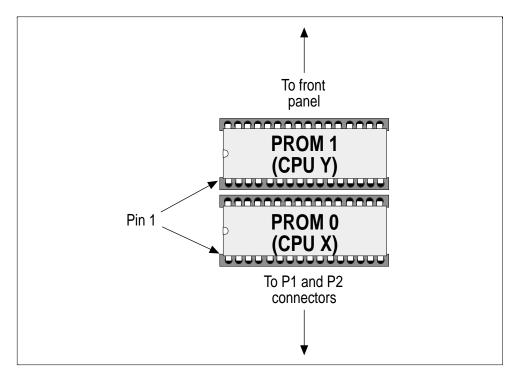

Monitor EPROM sockets and jumpers on V452 Series boards

The black triangle near the jumper block and connectors points to pin 1.

**Power-down and remove the CPU motherboard from the card cage** (if necessary) — Power-down the system and remove the V452 Series CPU board from the card cage.

Synergy CPU motherboards contain static-sensitive devices. Make sure you are properly grounded (by putting on a ground-strap, touching the system power supply, etc.) before removing and handling the board.

- **Output**Locate the current monitor PROM(s) or sockets on the CPU board and remove the current monitor PROM (if necessary) The figure on the previous page shows the location of the monitor PROM socket(s) and the monitor PROM configuration jumpers on V452 Series boards

- **4 Install the EPROM** Install the PROM in the appropriate socket. The PROM socket(s) on Synergy boards accept 32-pin PROM devices. The figure below shows the orientation of each PROM after proper installation.

EPROM devices properly installed in sockets

V452 User Guide 2-9

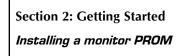

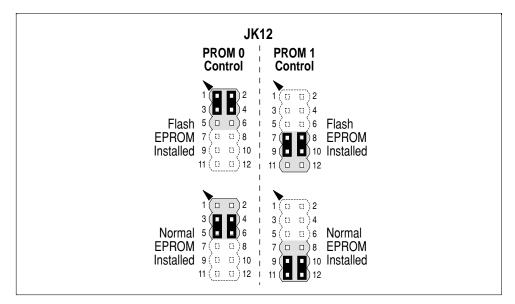

**Select the Monitor PROM type** (if required) — V452 Series boards provide two independent 32-pin, 8-bit sockets typically used for system firmware. These two sockets can accept 1 Mbit - 8 Mbit EPROM chips, 512 KB of Flash EPROM or a combination of these devices.

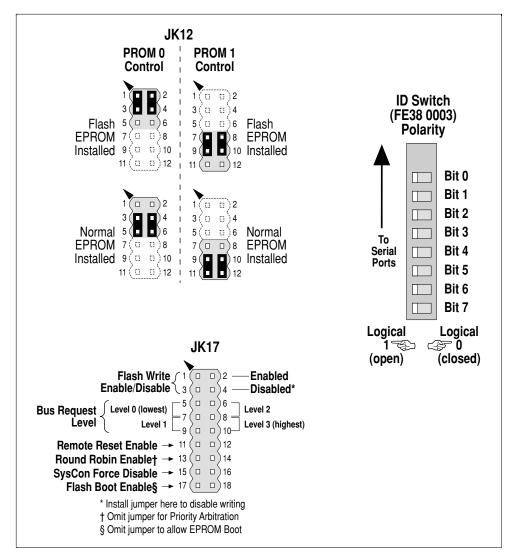

To indicate what type of PROM device is installed in each socket, configure the **JK12** jumper as shown in the figure below:

EPROM type jumper settings (JK12)

One of the shunt configurations shown above must be in place for proper operation of each PROM installed on the board.

Check the configuration of JK12 whenever a new EPROM or Flash PROM is plugged into the board.

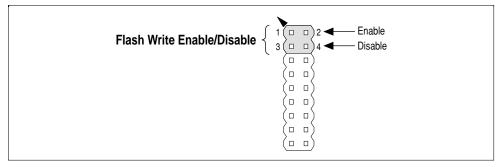

**6** Enable/disable Flash EPROM writes (if required) — Flash EPROM can be programmed using circuitry on the motherboard, allowing firmware code maintenance and updates to be performed across a network. If Flash EPROM has been installed on the board as described in Step **6** above, configure the **JK17** jumper as shown in the figure below:

#### Flash EPROM Write Enable/Disable

Disable\*

Enable\*

#### Flash EPROM Write enable/disable jumper settings (JK17)

Enabling Write enable function allows Flash EPROM writing to occur but does not actually start the process. For this activity to occur, a series of other software instructions must be executed which apply various power and data signals to the Flash EPROM chip.

For more information about on-board programming of Flash EPROM devices, see the datasheet for the Flash EPROM devices in the datasheet for the 28F010 Mbit Flash EPROM datasheet in the **Datasheet Supplement** supplied with this manual. The programming sequence described in this datasheet can be applied to both the **28F010** and the **28F020** device types. Also refer to the **EPROM** chapter in Section 4 and the **Flash EPROM programming tools** chapter in Section 6.

If Flash EPROM is installed in either or both of the PROM sockets, one of the shunt configurations shown above must be in place for proper operation. If Flash EPROM is not installed, no jumper is necessary.

To verify the proper operation of the newly installed EPROM, perform the procedure as described in the *Installing V452 Series CPU boards* chapter in this section.

<sup>\*</sup> Jumper must be installed as shown to disable writing.

# Section 2: Getting Started Installing a monitor PROM

# Installing the R452/R453 memory module

V452 Series boards provide all on-board DRAM on upgradable memory modules. Modules are available with the following amounts of DRAM:

- 4 MB

- 8 MB

- **9** 16 MB

- **9** 32 MB

- **9** 64 MB

- 128 MB

- 256 MB (special factory order)

- 512 MB (special factory order)

Normally, all V452 Series boards ship from the factory with a memory module installed. The modular design of the V452 Series DRAM interface, however, allows for easy DRAM upgrades in the field.

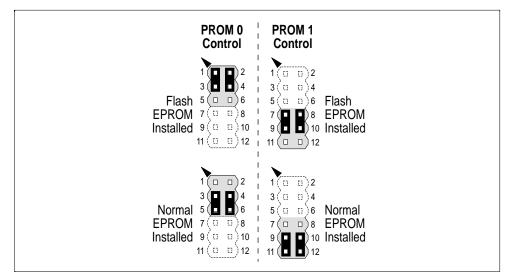

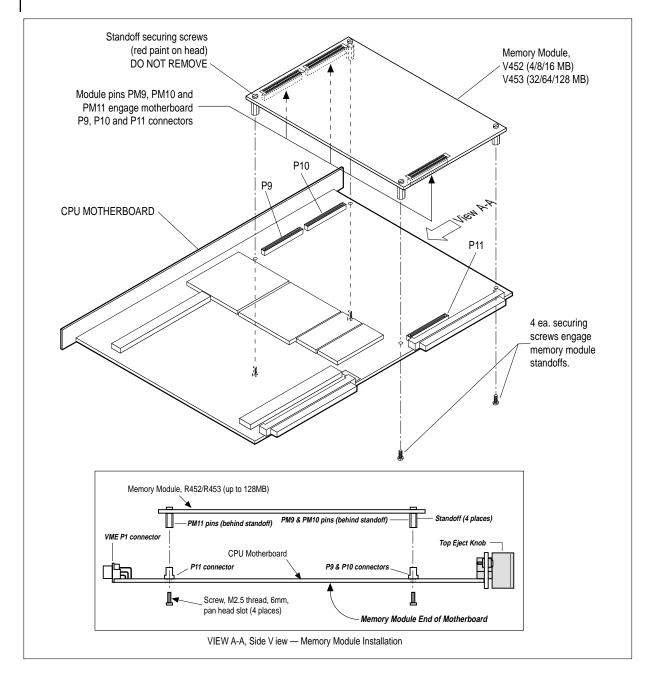

The drawing below shows the location of the R452/R453 memory module on the motherboard.

#### Installing the R452/R453 memory module

R452/R453 memory module location (top view)

This chapter describes field installation of an R452/R453 memory module.

If the desired R452/R453 module is already present on the V452 Series board, proceed to the next chapter in this section.

# Installing/upgrading the R452/R453 memory module

Perform the following steps to install or upgrade a R452/R453 memory module.

- Verify proper operation of motherboard (if replacing an existing R452/R453 memory module) Before attempting to install a new R452/R453 memory module on a working CPU motherboard, consider checking that the motherboard (and any attached EZ-bus modules) are operating properly.

- Perform the installation/checkout procedure for the V452 Series board as described later in this section.

- **Power-down and remove CPU motherboard from card cage** (if necessary) Power-down the system and remove the V452 Series CPU board from the card cage.

Synergy CPU motherboards contain static-sensitive devices. Make sure you are properly grounded (by putting on a ground-strap, touching the system power supply, etc.) before removing and handling the board. Use an ESD-protected workstation for module removal and installation work.

- Remove existing R452/R453 memory module from CPU motherboard (if you are replacing refer to drawing below for assembly details):

- a. Place V452/R45x assembly face-down, that is with large circuit board (motherboard) on top, on a flat surface of an ESD-protected workstation.

- b. Remove four M2.5 slot-head screws from rear (solder) side of V452 motherboard (area of P9, P10 and P11).

- c. Turn V452/R45x assembly over.

- d. Grasp R45x at sides and gently pull up until the connectors come loose.

#### Installing the R452/R453 memory module

R452/R453 module installation

4 Install R452/R453 module on motherboard — Installation of R452/R453 memory module is reverse of removal. Before installing, make sure that connectors are engaged before fully seating module. Refer to drawing on preceding pages for assembly details.

# Setting up the V452 Series hardware

This chapter lists the hardware configuration decisions and steps that need to be made before installing V452 Series boards.

Normally, boards are ordered and built for a particular application that establishes a configuration that encompasses many if not all of the configuration tasks described in this chapter.

As a result, because many of these set-up decisions are application dependent and/or already set by your ordering specification, this chapter seeks to **describe** the general hardware configurations rather than **prescribe** any particular system arrangement or suggest that the configuration of the board as sent from the factory **needs to be changed**.

Rather, it is intended as a summary/index of the required configuration steps, a *quick start* or *installer's checklist* for those who already have a working knowledge of the issues involved, and an introduction to the special features of the components or architecture on V452 Series boards.

This chapter refers to several operational subjects that in most cases are covered in more detail elsewhere in this manual. If more information on a particular subject is available, the descriptions in this chapter tell where it can be found.

#### Setting up the V452 Series hardware

## **Default configuration**

The table shown below lists the default hardware configuration for the V452 Series boards before any jumpers, shunts, or custom modifications are made.

#### Default hardware conditions

| Jumpers (presumes no jumper installed)                        | Description     |

|---------------------------------------------------------------|-----------------|

| JK17 — Flash write enable/disable                             | Disabled*       |

| — Bus Request Level                                           | Set by software |

| VME Remote Reset                                              | Disabled        |

| <ul> <li>Round Robin/Priority VME request handling</li> </ul> | Priority        |

| <ul><li>— Auto System Controller</li></ul>                    | Enabled **      |

| <ul> <li>— EPROM/Flash Boot select</li> </ul>                 | Flash boot      |

**Notes:** \* Default state is 'disabled' with no jumper installed, but input is floating. To guarantee write protection of flash memory, install jumper in disabled position.

# Configuration tasks

It may be necessary to change the default conditions listed in the table above by installing shunts on the appropriate jumper block. The required hardware configuration tasks are outlined below and described in more detail in the following pages:

- Verify that the board has a monitor EPROM and memory module installed.

- **2** Verify/install shunt at JK17 to enable or disable writing to Flash.

- Install a shunt at JK17 to set the bus request level (remove shunt for software control of bus request level).

- Install a shunt at JK17 to enable VME remote reset (if desired).

- Install shunt at JK17 to prevent the board from being set up as the VME System Controller as required.

- Install a shunt at JK17 to select Round Robin interrupt handling (only if the board is to serve as System Controller).

- Install a shunt at JK17 to select Flash for booting (remove shunt to boot from EPROM).

<sup>\*\*</sup> Board automatically set up as System Controller when installed in Slot 1 of card cage.

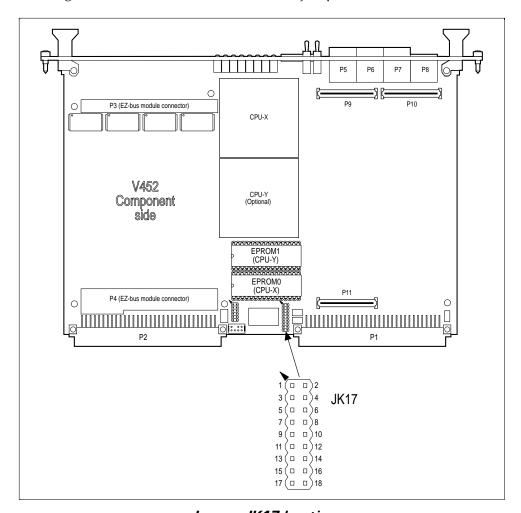

Several of these configuration tasks involve the **JK17** jumper block. The drawing below shows the location of this jumper block.

Jumper JK17 location

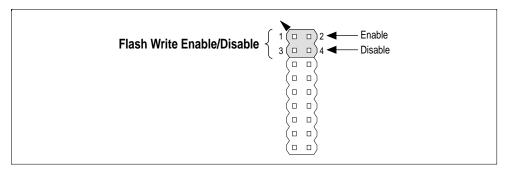

### Enable/Disable Flash write

Write protection of Flash memory installed in the V452 Series EPROM sockets is provided by two pair of jumper pins on JK17. To enable Flash write, install a shunt across JK17 pins **1** and **2**. To disable Flash write, install a shunt across JK17 pins **3** and **4**. The figure below shows the jumper pins controlling Flash write.

Jumper settings (JK17) - Flash write enable/disable

If no jumper is installed at all in either of the two positions, Flash writing is disabled by default, though input pins (Vpp) are left floating. To guarantee write protection, install a shunt across JK17 pins 3 and 4.

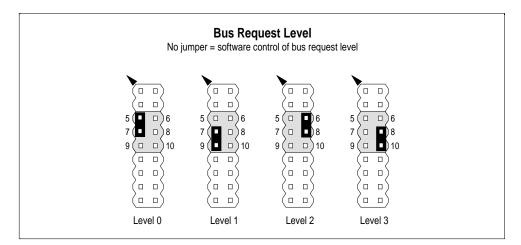

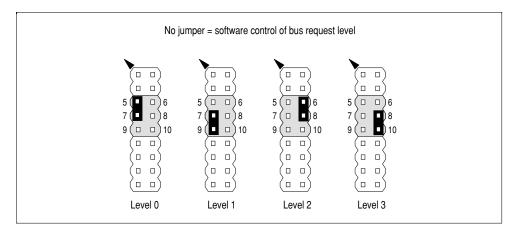

# Set the VMEbus request level

The VME interface on V452 Series boards can request access to the VMEbus at four different priority levels from lowest (level 0) to highest (level 3) priority. The V452 bus request level can be set in either hardware (JK17 jumpers) or software. If no bus request level jumpers are installed, the Ethernet/VMEbus control registers (FE3A 4000-F) take over to set the bus request level.

To set the bus request level in hardware, configure JK17 pins **5-10** for one of the bus request levels as shown in the figure below:

Bus request level jumper settings (JK17)

For more information about setting the bus request level in software, see the *V452 Series internal registers* chapter in Section 3. For more information about selecting a VMEbus request level, see the *VME Master interface* chapter in Section 5.

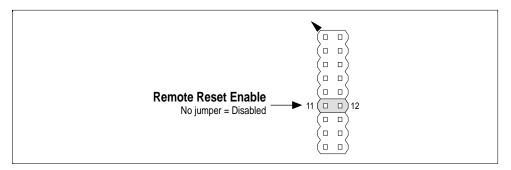

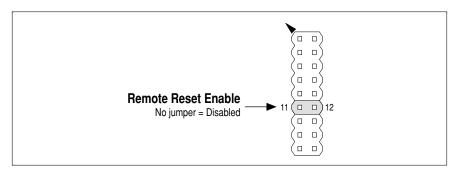

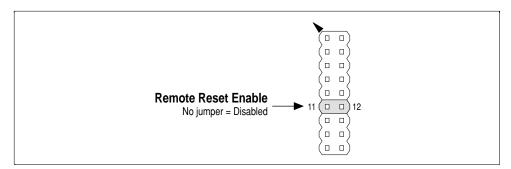

#### Enable VME Slave remote reset

V452 Series boards support remote reset by external VME Masters. To enable VME Slave remote reset, install a shunt across JK17 pins 11 and 12 as shown in the figure below. Remove the shunt to disable this feature (if necessary).

Jumper settings (JK17) - Remote Reset enable

For more information about VME remote reset, see the **Default and reset condi**tions chapter in Section 3 and the VME Slave interface chapter in Section 5

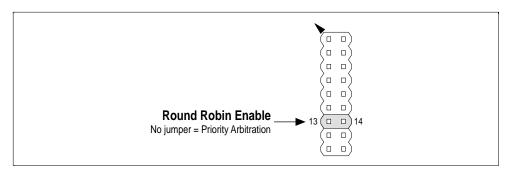

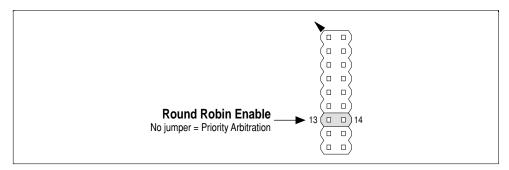

# Select Round Robin or Priority request handling

If acting as the System Controller, V452 Series boards can support either Round Robin or Priority handling of VMEbus requests.

To select **Round Robin** request handling, install a shunt across JK17 pins **13** and **14** as shown in the figure below. To select **Priority** handling remove this shunt (if it is installed).

Jumper settings (JK17) - Round Robin vs. Priority requests

For more information about these VMEbus request methods, see the **System Controller** chapter in Section 5.

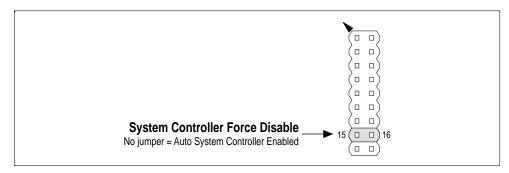

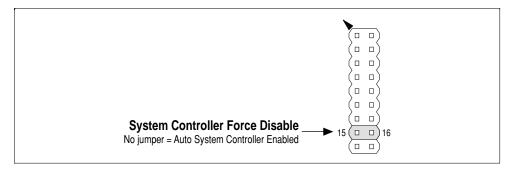

## System controller force disable

All V452 Series boards contain circuitry allowing them to automatically serve as the System Controller on the VMEbus when installed in slot 1.

A jumper is provided to force disable of the system controller. Normally, this jumper is not installed. However, in the event of unwanted interactions with the auto-detection circuitry, force the system controller to the disabled state by installing a shunt across JK17 pins **15** and **16** as shown in the figure below.

Jumper settings (JK17) - System Controller force disable

For more information about the capabilities and features of the V452 Series System Controller circuit, see the **System Controller** chapter in Section 5.

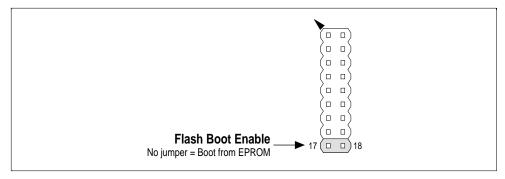

### Boot select, EPROM or onboard Flash

A jumper is provided to select between booting from EPROM socket devices (i.e., regular EPROM or Flash EPROM) or the onboard Flash memory. As shown in the figure below, install a shunt across JK17 pins 17 and 18 to boot from Flash. To boot from EPROM, remove the shunt from JK17 pins 17 and 18.

Jumper settings (JK17) - EPROM/Flash boot select

With no jumper installed at JK17 pins 17 and 18, the CPU reads its reset vector from EPROM0 at FE00 0000. When this jumper is installed, the CPU reads its reset vector from the onboard Flash memory at FC00 0000.

# Section 2: Getting Started

## Setting up the V452 Series hardware

# Installing V452 Series CPU boards

This chapter explains how to install an V452 Series board in a VME card cage.

#### **Materials**

To complete this procedure, you will need the following materials:

- V452 Series board to be installed,

- VME card cage meeting the minimum system requirements (See the chapter on *Minimum system requirements* earlier in the *Getting Started* section.)

## Procedural steps

To install the V452 Series boards in a VMEbus card cage, perform the following steps:

● Install the board in a VMEbus slot — if the board is to be the System Controller, install it in Slot 1.

If you intend to install the board in a slot that has been empty up to this point, be sure to remove the daisy-chain jumpers for that slot from the VMEbus. For more information, refer to the documentation accompanying the system or VMEbus card cage assembly you are using.

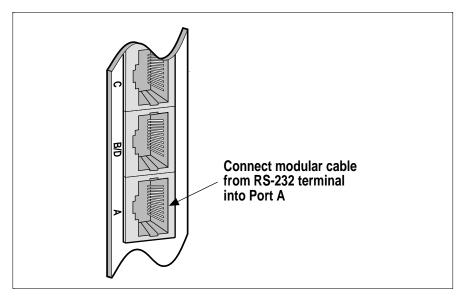

**Attach a modular serial interface cable to Serial I/O connector A on the front panel** — Once the board is installed, plug a modular serial I/O cable into the 10-pin, modular Serial I/O connector A (P5) on the front panel as shown in the figure below.

For more information, see the **Serial cabling options** chapter in Appendix A.

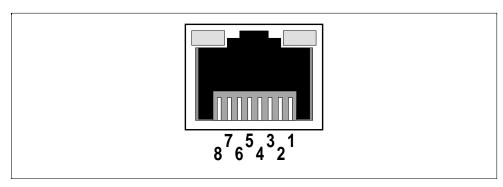

Serial I/O port A (front panel)

- **3 Connect terminal to I/O cable** − Connect an RS-232/423 or RS-422 compatible terminal to the serial I/O cable. Set the terminal communication configuration to:

- 9600 baud

- receive, no handshake

- transmit, Xon/Xoff

- no parity

- one stop bit

To allow the modular cable to connect to a D-type connector on the terminal, use a Modular/EIA adapter described in the **Serial cabling options** chapter in Appendix A.

Note that serial ports A and C can support either RS-232/RS-423 single ended or RS-422A signals to either DTE or DCE devices by using different interface cable and adapter configurations. Serial ports B & D support only RS-232/RS-423. To ensure that the cable/adapter you are using provides the required signals for your terminal or serial device, see the **Serial cabling options** chapter in Appendix A.

- Power-on all units Power-up the card cage containing the V452 Series board and the video terminal that is connected.

- **Verify boot sequence and appearance of start-up banner** Immediately upon power-up, all of the yellow LEDs on the board's front panel flash momentarily. Then, the green X LED should illuminate as the CPU accesses the boot PROM.

The start-up banner for the monitor PROM/EPROM you have installed on the board should then appear. If the banner appears, the V452 Series is in working condition and ready for user-configuration.

The power-up banners you may see are described below:

#### Power-on banners

The paragraphs below show example power-on banners for the various operating system PROM/EPROMs that are available for V452 Series boards. Note that firmware revisions may result in actual displays that differ from the given examples.

#### **OS-9**

Shown below is an example of the OS-9 PROM's power-up banner. For more information, see the *Using Professional OS-9*, product documentation from Microware Systems Corporation or contact:

OS-9/68000 Operating System Microware Systems Corporation 1900 N.W. 114th Street. Des Moines, Iowa 50322 (515) 224-1929

In the below example of the OS-9 startup banner, the user must enter a **g <Enter>** in response to the **RomBug:** prompt in line 11 to see the remainder of the banner. The last six lines of the banner also includes a login routine in which user input is required.

```

OS-9/68K System Bootstrap

<Called>

Searching special memory list for symbol modules...

rombug40X_8M

an: FE000AAC FE000500 FE040000 FE040000 0000C200 00004000 0000B200 0000B1F0

pc: FE0009AE sr:2708 (--SI-7-N---)t:OFF msp:00039172 usp:00000000

Boot

>43FAFBAC

lea.l Reset(pc),a1

RomBug: g

BOOTING PROCEDURES AVAILABLE ---- <INPUT>

Boot from Viper tape drive ----- <vs>

Boot from SCSI(SCCS) hard drive - <hs>

Boot from ROM ----- <ro>

Load Bootfile from ROM ----- <lr>

Synergy Ram Boot ---- <ra>

Boot from BOOTP I82596 ----- <ie>

Reconfigure the boot system ---- <rc>

Restart the system ----- <q>

Select a boot method from the above menu: hs

A valid OS-9 bootfile was found.

-t -np

OS-9

Copyright 1984 by Microware Systems Corporation

The commands in this file are highly system dependent and should

be modified by the user.

;* start system clock

December 11, 1996 Wednesday 10:55:27 am

iniz /h0

*chd /h0/SYS

*startisp

*chd /h0

* iniz r0 h0 d0 t1 p1 ;* initialize devices

;* make some utilities stay in memory

;* get the default device descriptor

* init.ramdisk >/nil >>/nil& ;* initialize it if its the ram disk

* tsmon /t1 &

;* start other terminals

* list sys/motd

ex tsmon /term

1 devices online

OS-9/68K V3.0.2 Synergy Microsystems SV40 - 68040 96/12/11 10:55:32

User name?: super

Password:

Process #06 logged on 96/12/11 10:55:35

Welcome!

Super>

```

### pSOS/pROBE (pSOS+/68k)

Shown below is an example of the pSOS/pROBE PROM's power-up banner. For more information see the pSOS<sup>+</sup>/68k Evaluation Package User's Guide; Manual Version 1.1; Software Components Group or contact:

Synergy Microsystems, Inc. (858) 452-0020

OR

Software Components Group, Inc 1731 Technology Drive, Suite #300 San Jose, CA 95110 (408) 437-0700

PROBE V3.14 (68040)

COPYRIGHT 1986, SOFTWARE COMPONENTS GROUP INC.

ALL RIGHTS RESERVED

PROBE>

#### pROBE.jr (pROBE/68k)

Shown below is an example of the pROBE.jr PROM's power-up banner. For more information, see *pROBE.jr User Guide*; Synergy Microsystems, Inc., or contact:

Synergy Microsystems, Inc. (858) 452-0020

OR

Software Components Group, Inc 1731 Technology Drive, Suite #300 San Jose, CA 95110 (408) 437-0700

Synergy Microsystems Inc. pROBE.jr v3.1.0 DebugMon Software Components, Inc <board/mod> - mm/dd/yy

pROBE.jr:

#### **VxWorks**

Shown below is an example of the VxWorks PROM's power-up banner. For more information see the *VxWorks Reference Manual*; Version 5.2; Wind River Systems or contact:

Synergy Microsystems, Inc. (858) 452-0020

OR

Wind River Systems, Inc. 1351 Ocean Ave. Emeryville, CA 94608 (800) 545-WIND

# Section 2: Getting Started Installing V452 Series CPU boards

```

boot device

ei

processor number

: 0

: host

host name

file name

: /vw/trg/sv462x

inet on ethernet (e): 197.42.42.225:ffffff00

inet on backplane (b): 198.0.0.1

host inet (h)

: 197.42.42.10

user (u)

: vw

: 0x0

flags (f)

Attaching network interface ei0... done. Subnet Mask: 0xffffff00

Attaching network interface 100... done. Loading... 490048 + 30480 + 24382

Starting at 0x1000...

Target Name: vxTarget

Attaching network interface ei0... done.

Initializing backplane net with anchor at 0x600... done.

Backplane anchor at 0x600... Attaching network interface sm0... done.

Attaching network interface lo0... done.

Loading symbol table from host:/vw/trg/sv462x.sym ...done

]]]]]]]]]

]]]]

(R)

]]]]]]]]

]]]]

]]]]]]]]

1111111

1111111111

]]]]

]]]]

]]]]

],;

]] ]]]]]]]

]]]]]

]]]]]

]] ]]]]

]]]]]]]

]]]]

]] ]]]]

]] ]]]]

11111

]]]]]]

] ]]]]]

111111111

]]]]

]]]

]]]]

1111 11111

]]]]

]]]]]]]

]]]]

1111 1111 11111

]

11111111111111111111111111111111111

Development System

VxWorks version 5.2

KERNEL: WIND version 2.4

Copyright Wind River Systems, Inc., 1984-1995

CPU: Synergy SV-462x. Processor #0 0x200000000[0x200000] BSP version 1.0/4 Friday Nov 17, 1995 <15:44:17> GMT

->

```

#### Installing V452 Series CPU boards

#### **SMon**

Shown below is an example of the SMon PROM's power-up banner. For more information see the SMon User Guide or contact:

Synergy Microsystems, Inc. 9605 Scranton Road, Suite 700 San Diego, CA 92121-1773

| SMon BOOT ROM V2.65 (Synergy Microsystems - SV400/440/460 X CPU)                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copyright (c) 1992,1993,1994, Synergy Microsystems, Inc.                                                                                                                                                                         |

| HARDWARE PARAMETERS:  This Board's address on the VME bus is 0x02000000  The serial channel will use a baud rate of 9600  POWERUP TEST(S):  Powerup test(s) are disabled  After board is reset, startup code will wait 2 seconds |

| To change any of this, hit any key within 2 seconds                                                                                                                                                                              |

|                                                                                                                                                                                                                                  |

| Synergy V4X0 Monitor & C Compiler Rev 2.65, 1994/06/28                                                                                                                                                                           |

| Type "help" for help.                                                                                                                                                                                                            |

| hello world                                                                                                                                                                                                                      |

| Aug 12 12:02:26 1994<br>SMon>                                                                                                                                                                                                    |

# Setting up the V452 Series software

Upon power-up, V452 Series boards require a set of software instructions to set up several on-board functions. The monitor EPROM that may be provided with the V452 Series board establishes a particular initialization or environment encompassing many if not all of these initialization tasks.

Because many of these set-up decisions are application-dependent and/or already set by your system firmware, this chapter seeks to **describe** the general requirements for system initialization rather than **prescribe** any particular system arrangement or to suggest that any changes need to be made to the software configuration provided by the system software package that may have been supplied with the board.

This chapter describes the general default or pre-initialized state of V452 Series boards following a power cycle or board reset and then goes on to describe the required and/or optional software initialization tasks needed to bring the board up from scratch. It is intended to serve as a summary/index of the required configuration steps, a *quick start* or *programmers checklist* for those who already have a working knowledge of the issues involved, and an introduction to the special features of the components or architecture of V452 Series boards.

This chapter refers to several operational subjects that in most cases are covered in more detail elsewhere in this manual. If more information on a particular subject is available, the descriptions in this chapter tell where it can be found.

# Section 2: Getting Started Setting up the V452 Series software

# Default (pre-initialization) conditions

V452 Series boards present a series of default conditions that exist before software initialization occurs. To provide maximum flexibility, V452 Series boards provide several software initialization registers to set up the board for a specific use. Some of these conditions are unique to the V452 Series architecture/circuitry while others pertain to individual chips. The following table lists these pre-initialization conditions.

#### Default conditions on power-up

| Front panel LEDs                                               |                          |  |  |  |  |

|----------------------------------------------------------------|--------------------------|--|--|--|--|

| Application LEDs (front panel)                                 | On                       |  |  |  |  |

| Fail LED                                                       | On                       |  |  |  |  |

| On-board interrupts                                            |                          |  |  |  |  |

| ABORT switch (Level 7 interrupt)                               | Enabled (non-maskable)   |  |  |  |  |

| Status for all other Interrupt sources (Levels 7 - 2)          | Disabled                 |  |  |  |  |

| 68040/060 functions                                            |                          |  |  |  |  |

| Internal cache contents                                        | Indeterminate            |  |  |  |  |

| Internal instruction & data caches                             | Disabled                 |  |  |  |  |

| Memory areas not subject to caching (transparent translation)  | None                     |  |  |  |  |

| On-board DRAM                                                  |                          |  |  |  |  |

| Content of on-board RAM and RAM parity                         | Indeterminate            |  |  |  |  |

| Memory parity checking                                         | Disabled                 |  |  |  |  |

| CPU Watchdog                                                   |                          |  |  |  |  |

| CPU Watchdog Halt monitor                                      | Disabled                 |  |  |  |  |

| CPU Watchdog Run monitor                                       | Disabled                 |  |  |  |  |

| Serial ports B & D                                             | Disabled                 |  |  |  |  |

| EPROM1 access by CPU-Y                                         | Enabled                  |  |  |  |  |

| VME Slave interface                                            |                          |  |  |  |  |

| Slave interface status                                         | Disabled                 |  |  |  |  |

| Slave memory write access                                      | Disabled                 |  |  |  |  |

| Slave memory write access protection level                     | Supervisor-only          |  |  |  |  |

| Address width                                                  | A32                      |  |  |  |  |

| Window size                                                    | 16 MB                    |  |  |  |  |

| Base Address                                                   | 0 MB (x000 000)          |  |  |  |  |

| Lower vs. Upper VME A32/D32 address range                      | Lower (Top of DRAM to    |  |  |  |  |

|                                                                | 0x3FFF FFFF)             |  |  |  |  |

| VME Master interface                                           |                          |  |  |  |  |

| VMEbus release configuration                                   | Release on Request (ROR) |  |  |  |  |

| VMEbus request configuration                                   | Not FAIR requests        |  |  |  |  |

| VMEbus request level configuration (if not set by JK17 jumper) | Level 3                  |  |  |  |  |

| VME interrupts                                                 |                          |  |  |  |  |

| VME Interrupter status                                         | Reset                    |  |  |  |  |

| VME interrupt level asserted by the VME interrupter            | Level 7                  |  |  |  |  |

| VME interrupt vector asserted by the VME interrupter           | Indeterminate            |  |  |  |  |

| VME Interrupt handler level                                    | None                     |  |  |  |  |

| VME SysRes signal                                              |                          |  |  |  |  |

| VME SysRes (reset) reception respond/ignore                    | Respond                  |  |  |  |  |

| VME SysFail signal                                             |                          |  |  |  |  |

| VME SysFail interrupt reception (via 2692 DUART)               | Disabled                 |  |  |  |  |

| VME SysFail\ signal                                            | Asserted                 |  |  |  |  |

| 2692 control registers                                         |                          |  |  |  |  |

| Serial ports B and D                                           | Disabled                 |  |  |  |  |

| VME interrupter level                                          | Level 7                  |  |  |  |  |

| SysFail reception                                              | Off                      |  |  |  |  |

#### Initialization tasks

The default conditions listed in the table above can be changed, if required, by executing an initialization program sequence during the system boot process. The same instructions from this sequence can also be used to alter settings *on-the-fly* to produce special environments or temporary effects.

The primary software initialization tasks are:

- Set up the 68040/060 caches & data fetching behavior,

- Enable the desired on-board and VME interrupts and configure the VME interrupter,

- 3 Initialize on-board devices,

- 4 Enable serial channels B and D (if desired),

- Turn off the application LEDs,

- Initialize RAM, clear parity, and enable memory parity protection (if desired),

- Set up the VME Master interface (if needed),

- **3** Set up and enable the VME Slave interface (if needed),

- Perform self test (if desired), release the VME SysFail signal, and turn off the Fail LED,

- Set up and enable Watchdog timer (if desired).

The remaining paragraphs in this chapter describe these software initialization tasks in greater detail.

#### Set up the CPU caches & data fetching behavior

The 68040/060 implements data and instruction caching to improve performance.

**Flushing the cache contents** — A power cycle or processor reset does not invalidate the cache lines. The caches, therefore, must be invalidated early in the initialization sequence to flush out old instructions and data. This is done with the 68040 CINVA assembler instruction which explicitly clears the cache:

cinva nop

If you do not have assembler that specifically supports the 68040, the following "hand-assembled" command can also be used:

# .short 0xF4DB nop

The **nop** instruction is recommended by Motorola to resynchronize the CPU's internal pipelines.

**Using the Transparent Translation register** — Certain types of data are not compatible with the CPU's caching and processing techniques. The Transparent Translation register in the CPU identifies areas in memory to be "translated" directly or given special handling by the CPU's MMU. The address space assigned to I/O functions is a particularly important area for such special treatment for the following two reasons:

- I/O areas are not compatible with data caching because the data they contain can be changed by an external source without the knowledge of the CPU's cache circuitry.

- Normally, I/O activity must be processed in a strict sequence of steps. Unless otherwise instructed by the MMU, the 68060 will choose the order of read and write instructions to optimize its own operations without regard for the needs of external devices.

As a result, the data (dtt0) in I/O regions (above **0xFE00 0000** on V452 Series boards) must be identified for "serialized" processing and must be inhibited from data caching using the following set of 68040 assembler commands:

Setting up the V452 Series software

movel #0xFE01C040, d0 movec d0. dtt0

The hexadecimal expression in the **movel** instruction given above directs the 68060 to perform the following individual actions:

- The **FE** byte designates the 16 MB area from 0xFE00 0000 to 0xFEFF FFFF as the base area for transparent translation.

- **2** The **01** byte designates an additional 16 MB area above the base area (0xFF00 0000 to 0xFFFF FFFF) for transparent translation.